# High Performance Current-Mode Multiplier Circuit based on Carbon Nanotube Transistors

# Mohammad Bagher Heidari, Zoheir Kord Rostami

Abstract— Abstract— Carbon Nanotube Field Effect Transistor (CNFET) is a promising new technology that overcomes several limitations of traditional silicon integrated circuit technology. In recent years, the potential of CNFET for analog circuit applications has been explored. This paper proposes a novel four quadrant analog multiplier design using CNFETs. The simulation based on CNFET technology shows that the proposed multiplier has better features than CMOS Multiplier. Multiplier-divider circuits is using in digital signal processing base on neural networks and communications (amplifiers with variable gain, modulators, detectors and,...).In Most of CMOS analog circuit, transistors are only in triode or saturate regions; till now both regions not used. In this one kind of current mode multiplier- divider circuits is intrudused.it is very simple, has low die area and wide range in low voltage. all tough this circuit has no sense to temperature variation and varying parameters.

Index terms—CNT ,Analog signal processing, current-mode operation, multiplier, reconfigurable circuits

#### I. INTRODUCTION

Signal processing circuits find a multitude of plications in many domains such as telecommunications, medical equipment, hearing devices, and disk drives [1]-[4], the preference for an analog approach of signal processing systems being mainly motivated by their low-power operation and high speed that allows a real-time signal processing.Multiplier circuits represent intensively used blocks in analog signal processing structures. The motivation for designing these computational structures is related to their extremely wide range of applications in analog signal processing, such as adaptive qualization, frequency translation, waveform generation and curve- fitting generators, amplitude modulation, automatic gain control, squaring and square rooting, rms-dc conversion, neural networks, and VLSI adaptive filters, or measurement equipment. Based on subthreshold-operated MOS transistors, the realization of multiplier/dividers [5]–[10] requires simple architectures. In order to improve the frequency response of the computational structures and to increase their -3 dB bandwidth, many analog signal processing functions can be achieved by exploiting the squaring characteristic of MOS transistors biased in saturation. In [11]-[15], multiplier structures were presented with single-ended input voltages, the linearization of their characteristics being obtained using proper squaring relations between the input potentials.

## Manuscript Received on June 2014.

**Mohammad Bagher Heidari**, Department of Electrical Engineering, Bushehr branch, Islamic Azad University, Bushehr, Iran.

**Dr. Zoheir Kord Rostami**, Department of Electrical Engineering, Shiraz University of Technology, Shiraz, Iran.

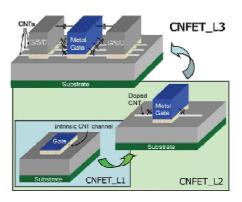

In order to implement the multiplication of two differential-input voltages, in [16]-[18] multiplier circuits were described based on mathematical principles, similar to the methods used for multipliers with single-input voltages. As one of the promising new transistors, carbon nanotube field-effect transistor (CNFET) overcomes most of the fundamental limitations of traditional silicon MOSFET. The excellent device performance of carbon nanotube (CNT) is attributed to its near-ballistic transport capability under low voltage bias [2]. Intense research on carbon nanotube (CNT) technology has been performed on digital circuit applications such as logic or memory, as well as radiofrequency (RF) devices for analog applications. The potential for high intrinsic device speed [3] and demonstration of CNFETs with a cut-off frequency fT as high as 80 GHz [4] have indicated that CNT-based devices are well suited as building blocks of future analog and RF circuits. CNFET structure is similar to a conventional MOSFET except that its semiconducting channel is made up of carbon nanotubes (CNT) as shown in Figure 1. Since the electrons are only confined to the narrow nanotube, the mobility goes up substantially on account of near-ballistic transport as compared to the bulk MOSFET. The near-ballistic transport is due to a limited carrier-phonon interaction because of larger mean free paths of acoustic phonons [5]. Additionally, CNFET shows higher current density, and higher electron mobility of the order of 104–105 cm2/Vs [6] compared with 103 cm2/Vs for bulk silicon.

Figure 1. CNFET device structure with multiple nanotubes (CNFET\_L3) and with a single tube (CNFET\_L2) as illustrated in [2].

The sizing of a CNFET is equivalent to adjusting the number of tubes. Since the mobility of n-type and the mobility of p-type carriers inside CNTs are identical, the minimum size is 1 for both P-CNFET and N-CNFET [7]. The device is turned

on or off by the applied gate voltage. Thus, CNFET is a high quality semiconducting material.

The potential of CNFETs for analog circuit design is explored in recent works [7,8]. CNFET also exhibits properties of higher current densities, higher transconductance, lower intrinsic capacitances, as compared to CMOS, which makes CNFET attractive for linear analog circuit applications. It has been demonstrated that CNFETs have the potential to provide higher linearity as compared to silicon or III-V semiconductors [9]. Therefore, low power and high bandwidth analog circuits can be designed based on CNFET. The four quadrant analog multiplier circuit is a versatile building block used for numerous communication signal processing applications. In contemporary VLSI chips, the analog CMOS multipliers are widely applied in phase-lock loops, automatic variable gain amplifiers, mixers, modulators, demodulators and many other non-linear operations - including division, square rooting, frequency conversion, etc. In most of applications, the desired multiplier's features are good isolation between input-output ports (especially for RF systems), wide input dynamic range, wide bandwidth, symmetric input/output delay, low power dissipation and low voltage supply [10]. Following the early work of Gilbert [11], a variety of multipliers has been designed with different optimization objectives [12-15]. Multipliers have been built around various topologies using Bipolar, CMOS [12,13] and Bi-CMOS [14,15] based circuits. The general idea behind these designs is to utilize electronic devices like BJT or MOS transistors to process the two input signals, followed by a cancellation of errors caused by non-linearity of the devices. MOS transistors are widely used for multiplication process, while differential circuit structure is generally used for nonlinearity cancellation [1D].

## II. THEORETICAL ANALOG ANALYSIS

Original implementations of current-mode multiplier/ divider structure will be presented. The main goal of the proposed design is related to the accuracy of implemented function. The current-mode approach of the multiplier/divider circuits strongly increases its frequency response. A further advantage of the independence of the computational circuit' output currents on technological parameters is that it contributes to an important increase in the accuracy of the multipliers and dividers. Additionally, the operation of the proposed circuits is not affected by the temperature variations.

## A.Multiplier/Divider Circuit

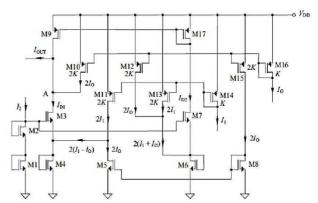

The second original realization of the multiplier/divider circuit is presented in Fig. 1. The equation of the functional loop containing M1, M2, M4, and M5 gate-source voltages can be expressed as follows:

$$2V_{GS}(I2) = VGS(I_{OUT1}) + V_{GS}[I_{OUT1} + 2(I1 + IO)]$$

(1)

Resulting

$$I_{\text{OUT1}} = I_2 - \frac{2(I_1 + I_O)}{2} + \frac{4(I_1 + I_O)^2}{16I_2}.$$

(2)

A similar expression can be obtained for the  $I_{OUT}2$  current, replacing in (4) the  $(I_1+I_O)$  current with  $(I_1-I_O)$  current. The expression of the output current of the multiplier/ divider

circuit from Fig. 2 is  $I_{OUT} = I_{OUT}1 - I_{OUT}2 + 2I_O$ , resulting  $I_{OUT} = (I_O\ I_1)\ /I2$ . The aspect ratios of MOS transistors from Fig. 2 are as follows: M1– M5, M7–M11, M13–M15, M18–M23 4.5/0.9; M6, M12 10.8/0.9; M16, M17 9/0.9. The chip area of the multiplier/divider implemented in 0.18- $\mu$ m CMOS technology, shown in Fig. 1, equals approximately 800  $\mu$ m2 (including pads). The negative feedback loops that enforce M4 and M15 transistors and, respectively, M8 and M18 transistors to have the same current are stable, since their speed is suitable for obtaining the requested frequency response for the designed circuits.

Fig. 2. Implementation of the multiplier/divider circuit.

## B.erors Introduced by Second-Order Effects

The most important errors introduced in the multiplier/ divider circuits' operation are represented by the mismatches, channel effect modulation, body effect, and mobility degradation. As a result of these undesired effects, the proper functionality of previous circuits will be affected by additive errors. The values of these errors are relatively small (because second-order effects are smaller with a few order of magnitude than the main squaring characteristic that models the MOS transistor operation). Additionally, a multitude of specific design techniques exist that are able to compensate the errors introduced by the second-order effects. The practical realization of translinear loops common-centroid MOS transistors strongly reduces the errors introduced by the mismatches between the corresponding devices. The design of current mirrors using cascade configurations allows an important reduction of the errors caused by the channel length modulation. In this situation, a tradeoff between the impact of the second-order effects and the minimal value of the supply voltage must be performed. Because the bulks of an important number of MOS transistors from Fig. 1 can be connected to their source (as a result of the original proposed circuit architectures), the errors introduced by the bulk effect can be canceled out for these devices.

## C. Small-Signal Frequency Response of Multiplier/ Dividers

The multiplier/divider circuit proposed in Fig. 1 is designed for allowing a high bandwidth. In order to achieve this goal, there exists a single high-impedance node, noted with A, which will impose the maximal frequency of operation. The frequency response of the multiplier/divider circuit presented in Fig. 2 is poorer than the frequency response of the circuit from Fig. 1, because in Fig. 2 there exist three high-impedance nodes (A, B, and C). As most of the nodes in

a circuit represent low-impedance nodes, it is expected that the proposed circuits to have relatively high maximal frequencies of operation (79.6 and 59.7 MHz, respectively, obtained after simulations).

#### III. SIMULATED RESULTS

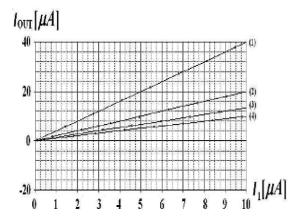

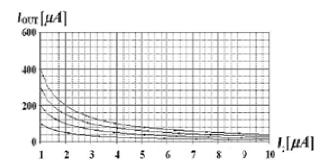

The IOUT (I1) simulation for the first multiplier/divider circuit proposed in Fig. 2, for an extended range of I1 current (between 0 and 10  $\mu$ A), is presented in Fig. 3. The IO current is set to be equal to 40  $\mu$ A, while the I2 current has a parametric variation: 1) 10  $\mu$ A; 2) 20  $\mu$ A; 3) 30  $\mu$ A; and 4) 40  $\mu$ A.

Fig. 3.  $I_{OUT}(I1)$  simulation for the multiplier/divider circuit

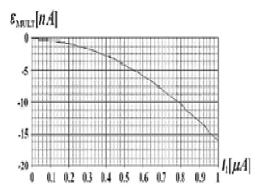

Fig. 4. Simulated linearity error for the multiplier/divider circuit.

The simulated linearity errors of the IOUT (I1) characteristic for the multiplier/divider circuits are shown in Fig4. The εMULT error is defined as the difference between the ideal linear characteristic of the multiplier/divider structure and its real characteristic, implemented using the original proposed computational structure. Taking into account PVT and Monte Carlo analysis (performed for 2 standard deviations), the linearity errors of the circuits are smaller than 0.75% (first smaller multiplier/divider) than 0.9% and (secondmultiplier/divider). The IOUT (I2) simulation is presented in Figs. 4. The IO current is set to be equal to 10  $\mu$ A, while the I1 current has a parametric variation: 1) 10  $\mu$ A; 2) 20  $\mu$ A; 3) 30  $\mu$ A; and 4) 40  $\mu$ A. The range of I2 current was chosen to be between 1 µA and 10 µA. The simulation of the multiplier/divider frequency response shows a -3 dB bandwidth of approximately 59.7 MHz.

Fig. 5.  $I_{OUT}$  (I2) simulation for the multiplier/divider circuit.

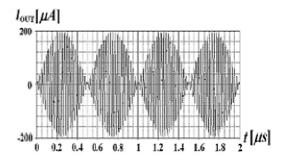

The transient analysis for the multiplier/divider circuit proposed in Fig. 2 is shown in Fig. 6. The IO current is a sinusoidal current with a frequency of 1 MHz and an amplitude equal to 200 µA, the I1 current is a sinusoidal current having a frequency of 60 MHz and an amplitude equal to 300  $\mu$ A, while I2 is a constant current equal to 300  $\mu$ A. The simulations were made using the BSIM4 model, associated with a 0.18-um CMOS process, MOS active devices having fT = 3.5 GHz. Comparing with alternative implementations in 0.35-um **CMOS** technology of the multiplier/divider structures, some important advantages can be achieved. The supply voltage can be decreased from 3 to 1.2 V, correlated with a relatively important decrease of the circuits' power consumption. Additionally, the circuits' bandwidths can be increased by their implementation in 0.18-µm CMOS technology. A comparison between the performances of multiplier circuits reported in the previous works and the multiplier/divider circuit in Fig.2 is presented in Table I. The proposed multiplier/divider structures have the most important advantages, such as the smallest linearity error and an increased bandwidth, compared with previously reported circuits. The circuits were designed for implementing in 0.18-µm CMOS technology, being supplied at 1.2 V. If the range of input currents is limited to  $0-5 \mu A$ , the power consumptions of both proposed multiplier/divider circuits (60 and 75 µW, respectively) are smaller than the power consumption of most previously reported circuits. The input referred noise is smaller than 0.6  $\mu$ V/  $\sqrt{Hz}$  for both proposed multiplier/divider structures.

Fig. 6. IOUT (t) simulation for the multiplier/divider circuit.

**Table I**Comparison Between The Proposed Ultiplier/Divider

Circuits and Previous Reported Works

| Reference | Technol       | Suppl | Linear | Power     | Bandwi |

|-----------|---------------|-------|--------|-----------|--------|

| no./Param | ogy           | у     | ity    | Consump   | dth    |

| eter      | [ <i>μ</i> m] | Volta | Error  | tion [µW] | [MHz]  |

|           |               | ge    | [%]    |           |        |

|           |               | [V]   |        |           |        |

| CNT       | 0.032         | 1.2   | 0.5    | 1.46      | 85     |

| based     |               |       |        |           |        |

| CMOS      | 0.18          | 1.2   | 0.75   | 60        | 79.6   |

| based     |               |       |        |           |        |

## IV. CONCLUSION

A novel analog multiplier using carbon nanotube FETs is proposed The current-mode operation of the proposed computational structures further increases the circuits' accuracy, while the removal of the impact of temperature variations on the circuits' operation additionally contributes to the increase of the multiplier/dividers' performances. High linearity and good noise performance has been achieved by well designed structure of multiplier and fine-tuned parameters of CNFET. The performance of the proposed multiplier is also compared with similar works on multiplier in CMOS technology.

## **REFERENCES**

- R. Harjani, "A low-power CMOS VGA for 50 Mb/s disk drive read channels," IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., vol. 42, no. 6, pp. 370–376, Jun. 1995.

- [2] A. Motamed, C. Hwang, and M. Ismail, "A low-voltage low-power wide rang CMOS variable gain amplifier," IEEE Trans. Circuits Syst. II.

- Analog Digit. Signal Process., vol. 45, no. 7, pp. 800–811, Jul. 1998.

[3] C. Popa, Synthesis of Computational Structures for Analog Signal Processing, New York, USA: Springer-Verlag, 2011.

- [4] C. Popa, Superior-Order Curvature-Correction Techniques for Voltage References, New York, USA: Springer-Verlag, 2009.

- [5] C. Popa, "Low-power CMOS bulk-driven weak-inversion accurate current-mode multiplier/divider circuits," in Proc. Int. Conf. Electr Electron. Eng., 2003, pp. 66–73.

- [6] C. Popa, "Computational circuits using bulk-driven MOS devices," in Proc. IEEE EUROCON Conf., May 2009, pp. 246–251.

- [7] C. Popa, "Logarithmic curvature-corrected weak inversion CMOS voltage reference with improved performances," presented at the 11th Int. Workshop on Thermal Investigations on ICs and Systems, Lake Maggiore, Italy, 2005.

- [8] C. Popa, "A new curvature-corrected voltage reference based on the weight difference of gate-source voltages for subthreshold-operated MOS transistors," in Proc. Int. Symp. Circuits Syst., 2003, pp. 585–588.

- [9] C. C. Chang and S. I. Liu, "Weak inversion four-quadrant multiplier and two-quadrant divider," Electron. Lett., vol. 34, no. 22, pp. 2079–2080, Oct. 1998.

- [10] M. Gravati, M. Valle, G. Ferri, N. Guerrini, and N. Reyes, "A novel current-mode very low power analog CMOS four quadrant multiplier," in Proc. 31st Eur. Solid-State Circuits Conf., Sep. 2005, pp. 495–498.

- [11] C. Popa, "High accuracy CMOS multifunctional structure for analog signal processing," in Proc. Int. Semicond. Conf., 2009, pp. 427–430.

- [12] C. Popa, "CMOS multifunctional computational structure with improved performances," in Proc. 33th Ed. Annu. Semicond. Conf., vol. 2. 2010, pp. 471–474.

- [13] C. Popa, "Multiplier circuit with improved linearity using FGMOS transistors," in Proc. Int. Symp. ELMAR 2009, pp. 159–162.

- [14] Y. H. Kim and S. B. Park, "Four-quadrant CMOS analogue multiplier," Electron. Lett., vol. 28, no. 7, pp. 649–650, Mar. 1992.

- [15] Y. K. Seng and S. S. Rofail, "Design and analysis of a +-1 V CMOS four-quadrant analogue multiplier," IEEE Proc. Circuits, Devices Syst., vol. 145, no. 3, pp. 148–154, Jun. 1998.

- [16] C. Sawigun and J. Mahattanakul, "A 1.5V, wide-input range, high bandwidth CMOS four-quadrant analog multiplier," in Proc. IEEE Int. Symp. Circuits Syst., May 2008, pp. 2318–2321.

- [17] C. Sawigun, A. Demosthenous, and D. Pal, "A low-voltage, low-power, high-linearity cmos four-quadrant analog multiplier," in Proc. 18th Eur. Conf. Circuits Theory Design, Aug. 2007, pp. 751–754.

- [18] C. Popa, "Improved linearity active resistor with controllable negative resistance," in Proc. IEEE Int. Conf. Integr. Circuits Design Technol., Aug. 2006, pp. 1–4.

- [19] C. Popa and A. M. Manolescu, "CMOS Differential Structure with Improved Linearity and Increased Frequency Response," in Proc. Int. Semicond. Conf., vol. 2. Sep.—Oct. 2007, pp. 517–520.

- [20] C. Popa, "Programmable CMOS active resistor using computational circuits," in Proc. Int. Semicond. Conf., Oct. 2008, pp. 389–392.

- [21] C. Popa, "Improved linearity CMOS active resistor based on the mirroring of the ohm law," in Proc. IEEE 17th Int. Conf. Electron., Circuits, Syst., Dec. 2010, pp. 450–453.

- [22] A. Naderi, H. Mojarrad, H. Ghasemzadeh, A. Khoei, and K. Hadidi, "Four-quadrant CMOS analog multiplier based on new current squarer circuit with high-speed," in Proc. IEEE EUROCON Conf., May 2009, pp. 282–287.

- [23] A. Naderi, A. Khoei, and K. Hadidi, "High speed, low power four quadrant CMOS current-mode multiplier," in Proc. IEEE Int. Conf. Electron., Circuits Syst., Dec. 2007, pp. 1308–1311.

- [24] A. M. Manolescu and C. Popa, "A 2.5GHz CMOS mixer with improved linearity," J. Circuits, Syst. Comput., vol. 20, no. 2, pp. 233–242, 2010.

- [25] S. I. Liu and Y. S. Hwang, "CMOS squarer and four-quadrant multiplier," IEEE Trans. Circuits Syst. I, Fundam. Theory Appl., vol. 42, no. 2, pp. 119–122, Feb. 1995.

- [26] S. A. Mahmoud, "Low voltage low power wide range fully differential CMOS four-quadrant analog multiplier," in Proc. 52nd IEEE Int. Midwest Symp. Circuits Syst., Aug. 2009, pp. 130–133.

- [27] C. Sawigun and W. A. Serdijn, "Ultra-low-power, class-AB, CMOS four quadrant current multiplier," Electron. Lett., vol. 45, no. 10, pp. 483–484, May 2009.